- #ALTERA QUARTUS II ADDER LAB HOW TO#

- #ALTERA QUARTUS II ADDER LAB GENERATOR#

- #ALTERA QUARTUS II ADDER LAB FULL#

- #ALTERA QUARTUS II ADDER LAB SOFTWARE#

Note: Through the remaining of the semester that you may use either the Quartus SignalTap II Logic Analyzer or an external lab LSA whenever I specify LSA.

#ALTERA QUARTUS II ADDER LAB GENERATOR#

If this latch is implemented in an FPGA that has 4-input lookup tables (LUTs), then only one lookup table is needed, as shown in Figure 3a. (During lab, this part of the design will be placed in the device and its performance verified with the help of the word generator and the LSA. A style of VHDL code that uses logic expressions to describe this circuit is given in Figure 2. Figure 1 depicts a gated RS latch circuit. But first we will show how storage elements can be created in an FPGA without using its dedicated flip-flops.

#ALTERA QUARTUS II ADDER LAB HOW TO#

We will show how to make use of these flip-flops in Part IV of this exercise. Also, you will be introduced to the Altera DE0 board, the Digilent Analog Discovery, and to the techniques of using an oscilloscope and logic state analyzer (LSA) to test a constructed digital circuit. Part I Altera FPGAs include flip-flops that are available for implementing a user’s circuit. Both designs will be synthesized in Quartus and simulated in ModelSim (Altera edition).

#ALTERA QUARTUS II ADDER LAB SOFTWARE#

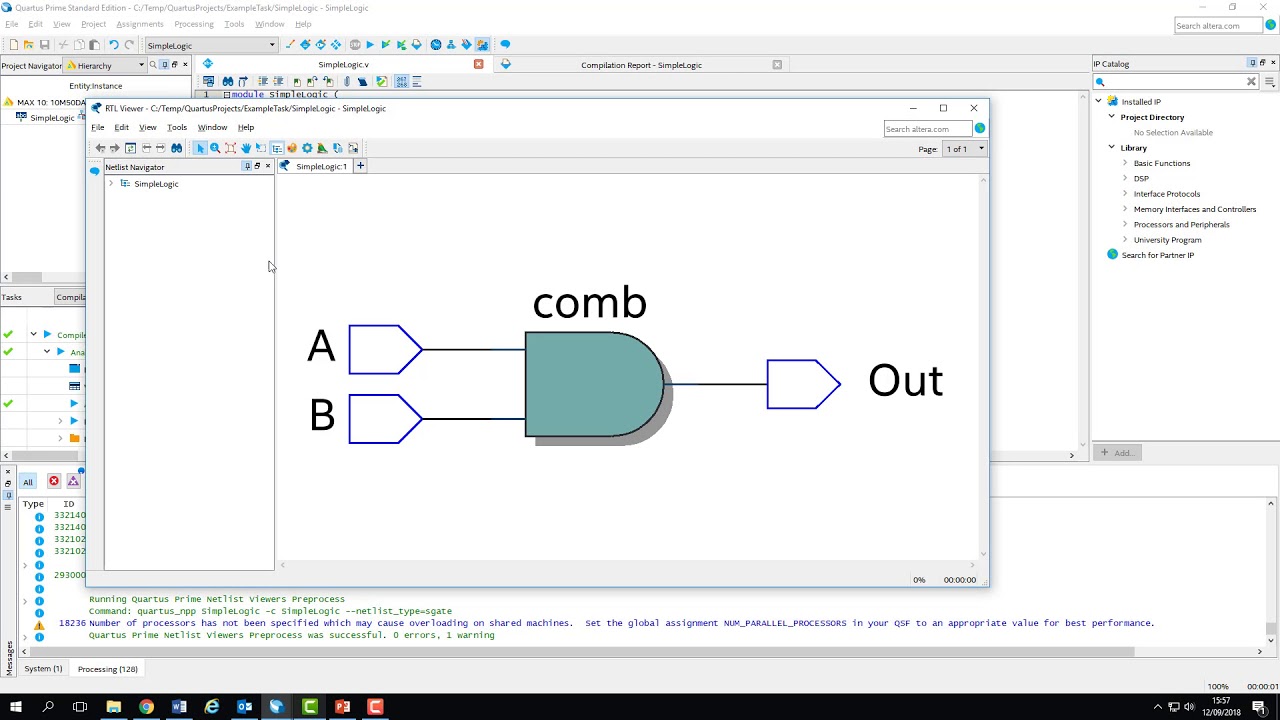

Regardless of whether you use a personal computer or a UNIX or Linux workstation, the Quartus II software ensures easy design entry, fast processing, and straightforward device programming. Enter a simple combinational logic circuit in VHDL using the Quartus II Text.

#ALTERA QUARTUS II ADDER LAB FULL#

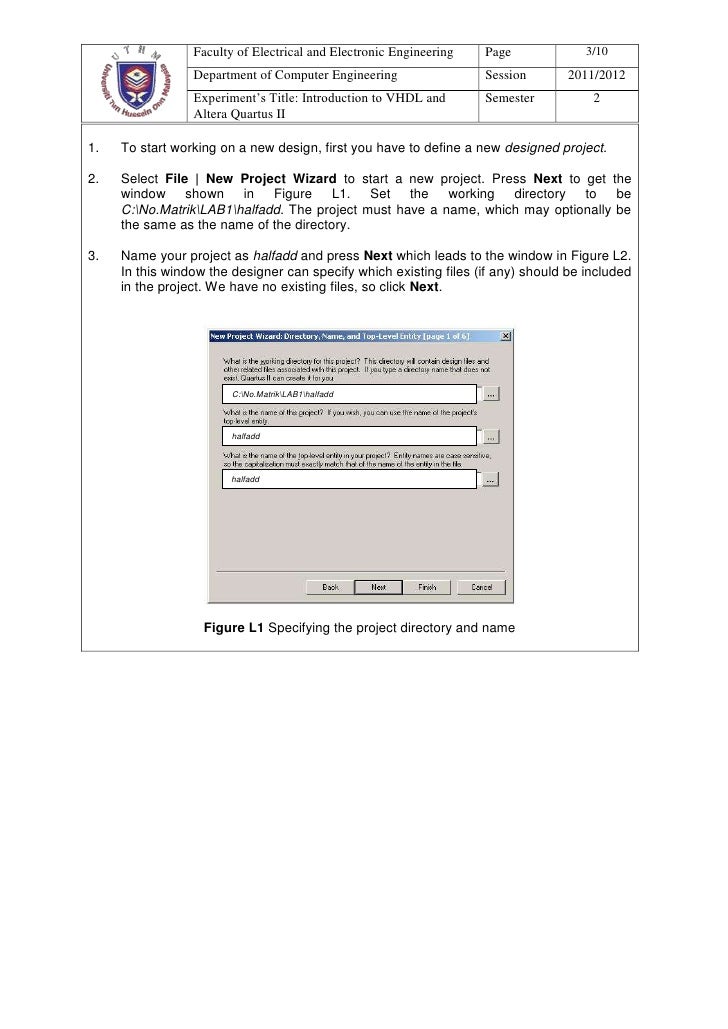

Modify your code from #2 above and implement and test the following circuit.Follow the instructions in the “Altera_FPGA_Tutorial.pdf” and then implement and test the two- input logic gates.Then, Read Sections 4.1, 4.2 and 4.3 carefully. Read the “DE1_User_Manual.pdf” before coming to Lab.Next we will add an Altera-based IP core to the project (formerly known as MegaCore). Create a new VHDL file called customip.vhdl and set it as your top-level entity. To become familiar with Verilog and the Altera Quartus-II FPGA compiler Create a Quartus II project called customip in your COE838 lab folder, setting up the necessary parameters for a HPS/FPGA system the Cyclonewith -V 5CSEMA5F31C6 device.

0 kommentar(er)

0 kommentar(er)